# RUNTIME SPECULATIVE SOFTWARE-ONLY FAULT TOLERANCE

#### YUN ZHANG

A DISSERTATION

PRESENTED TO THE FACULTY

OF PRINCETON UNIVERSITY

IN CANDIDACY FOR THE DEGREE

OF DOCTOR OF PHILOSOPHY

RECOMMENDED FOR ACCEPTANCE

BY THE DEPARTMENT OF

COMPUTER SCIENCE

ADVISER: PROFESSOR DAVID I. AUGUST

JUNE 2012

© Copyright by Yun Zhang, 2012.

All Rights Reserved

#### **Abstract**

Transient faults are emerging as a critical reliability concern for modern microprocessors. Recently, microprocessors have been designed with lower voltage level ,smaller and faster transistors enabled by improved fabrication technology. A combination of increased density of transistors on chip, reduced noise margin of each transistor, and voltage scaling are making hardware systems more susceptible to transient faults than ever.

Both hardware or software solutions have been proposed for transient fault tolerance. The hardware approach typically adds redundant hardware modules to the system, thus requiring extra chip area as well as higher hardware design and verification cost. In addition, the scope and mechanism of fault tolerance are hardwired at design time, which could be suboptimal with the change of deployment environment. Unlike hardware solutions, software-only techniques do not require any specialized hardware extensions and are more flexible with the scope of protection and the change of environment. However, even the best-performing software-only fault tolerance techniques incur significant performance cost. The overhead of prior work comes from doubled register usage, frequent inter-core communication, or barrier synchronizations. These factors prevent existing software techniques from being adopted widely.

To address these problems, this dissertation proposes Runtime Software-only Speculative Fault Tolerance (RSFT). The key insights behind this dissertation are: (1) not all values are equally important. Transient faults may alter a transistor's value, which is never used. Only the values that will affect the externally visible behavior of a program must be verified before being used; (2) Value speculation can efficiently remove data dependences introduced by cross checking values produced in the program and its redundant copy with high confidence, thus significantly improves program runtime performance.

RSFT serves as a virtual layer between the application and the underlying platform.

It takes a program binary and designated execution arguments as input, and automatically creates two symmetric program instances for redundant execution, to utilize extra cores in a multi-core system. RSFT detects transient faults at system calls level in a non-invasive way, and exploits high-confidence value speculation to achieve low runtime overhead. Light-weight runtime checkpointing and background validation work together to provide transient fault recovery with only 6.17% overhead. The prototype of this framework was implemented and evaluated on a commodity multi-core system. The evaluation demonstrated that with this framework, transient fault tolerance can achieve best-in-class performance, full fault coverage, and fast recovery with no hardware module involved.

#### **Acknowledgments**

First, I would like to thank my advisor David I. August for his guidance throughout my years in graduate school. His passion for research and his vision on research directions always give me great inspiration. David gave me priceless suggestions continuously on research, study and life, which I am and will always be grateful for. During the years I worked in his research lab, I learnt from him not only how to conduct research, how to write scientific papers, but also how to think and act like a real researcher. I am thankful for the opportunities and challenges he gave me all these years, which made this dissertation possible. I could not have made my way today without his encourage and support. I believe I will continue to benefit from the knowledge he taught me during my study in Princeton.

I thank Prof. David Walker and Prof. Scott Mahlke for reading this dissertation extensively and providing insightful comments. The dissertation was significantly improved based on their feedbacks. I would like to also thank Prof. Jennifer Rexford and Prof. Doug Clark for serving as my thesis committee members. Their feedbacks that helped me to polish and refine my thesis.

This dissertation would not have existed without the help and support from everyone in the Liberty Research Group. We engaged in numerous brainstormings, discussions, presentations throughout the years in graduate school. The collaborative environment of this group is extremely healthy and helpful. I have found great friendship with the Liberty group members. I will never forget the sleepless nights we spent together before paper deadlines and the coffee we shared.

I would like to first thank the senior Liberty group memebers, Neil Vachharajani, Matthew Bridges, and Guilherme Ottoni for their guide and help in my early years into my PhD study. I must also thank Thomas Jablin, for his intelligence throughout my years in Princeton. His broad knowledge in almost everything was certainly both inspiring and

educational. Without the discussions we had, this work would not have been possible. I am also indebted to Deep, who helped me on most of my paper submissions and magically made them better in every sense.

I also want to thank Prakash Prabhu, Souymadeep Ghosh, Jae W. Lee, Jialu Huang, Hanjun Kim, Nick Johnson, and Arun Raman, for making my life in graduate school an unforgettable experience. I will never forget the witty jokes Prakash tells everyday, the Bourburn shared with Nick when we are working for a paper deadline at midnight, and the countless lunch conversations with Jialu, and her talent in drawing.

During the years in Princeton, I had the luck to have great administrative support from the department and the Princeton University. In particular, my thanks go to Melissa Lawson, for handling my travelling, funding and many other things throughout the years. She made my life in Princeton a lot easier, which allowed me to focus on my research.

I also want to acknowledge the support from various organizations, who supported my PhD study. My work in Princeton was supported by DARPA, through contract FA8750-10-2-0253, the National Science Foundation through Grant No. 0627650 and 1047879, and the Gigascale Systems Research Focus Center, one of five research centers funded under the Focus Center Research Program, a Semiconductor Research Corporation program.

I would also like to thank my parents for their unconditional love and support, since I was a child. As the only child in the family, it was difficult for them to accept the fact that I have to spend so many years abroad studying, far away from home. But they supported me and my dream without reservation. They always encourage me to pursue what I love and are pround of my accomplishments. I cannot image how much they sacrificed to allow me to achieve what I have today. Everything I achieved today, is truly theirs.

Last, but not the least, I want to thank my husband Yunpeng Wang, for his love, care, and company during my last several years in graduate school. We met each other when I was failing in almost every aspect of my life. He brightens my life with humor, love and

great patience. I wish I could be half as witty and funny on my best days, as he is on his worst. I want to thank him for his unconditional support during highs and lows in our life together.

## **Contents**

|   | Abst | tract                                              | iii  |  |  |  |  |  |  |  |  |  |  |

|---|------|----------------------------------------------------|------|--|--|--|--|--|--|--|--|--|--|

|   | Ack  | knowledgments                                      |      |  |  |  |  |  |  |  |  |  |  |

|   | List | of Figures                                         | viii |  |  |  |  |  |  |  |  |  |  |

| 1 | Intr | oduction                                           | 1    |  |  |  |  |  |  |  |  |  |  |

|   | 1.1  | Limitations of Existing Fault Tolerance Techniques | 2    |  |  |  |  |  |  |  |  |  |  |

|   | 1.2  | Research Objectives and Contributions              | 4    |  |  |  |  |  |  |  |  |  |  |

|   | 1.3  | Dissertation Organization                          | 8    |  |  |  |  |  |  |  |  |  |  |

| 2 | Bacl | kground                                            | 9    |  |  |  |  |  |  |  |  |  |  |

|   | 2.1  | Transient Faults Problem                           | 9    |  |  |  |  |  |  |  |  |  |  |

|   | 2.2  | Existing Methods for Transient Fault Tolerance     | 12   |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.1 Hardware Redundancy                          | 12   |  |  |  |  |  |  |  |  |  |  |

|   |      | 2.2.2 Software Redundancy                          | 15   |  |  |  |  |  |  |  |  |  |  |

|   | 2.3  | Limitations of Existing Techniques                 | 18   |  |  |  |  |  |  |  |  |  |  |

| 3 | Run  | time Speculative Transient Fault Detection         | 21   |  |  |  |  |  |  |  |  |  |  |

|   | 3.1  | Related Work                                       | 22   |  |  |  |  |  |  |  |  |  |  |

|   | 3.2  | Overview                                           | 23   |  |  |  |  |  |  |  |  |  |  |

|   | 3.3  | Automatic Process Duplication                      | 24   |  |  |  |  |  |  |  |  |  |  |

|   | 3.4  | System   | Call Trapping                         | 25 |

|---|------|----------|---------------------------------------|----|

|   | 3.5  | Specul   | ation                                 | 27 |

|   | 3.6  | Misspe   | eculation Detection and Recovery      | 28 |

|   | 3.7  | Virtual  | Memory Space Synchronization          | 30 |

|   | 3.8  | Signal   | Handling                              | 32 |

|   | 3.9  | Option   | al Memory Page Walking                | 33 |

|   | 3.10 | Transie  | ent Fault Detection                   | 34 |

|   | 3.11 | Windo    | w of Vulnerability                    | 36 |

| 4 | RSF' | T Trans  | sient Fault Recovery                  | 37 |

|   | 4.1  | Transie  | ent Fault Recovery                    | 38 |

|   | 4.2  | Existin  | g Techniques and Limitations          | 39 |

|   |      | 4.2.1    | Program Re-execution                  | 39 |

|   |      | 4.2.2    | K-Modular Redundancy                  | 39 |

|   |      | 4.2.3    | Checkpointing                         | 41 |

|   | 4.3  | RSFT-    | Recover                               | 41 |

|   |      | 4.3.1    | Structural View                       | 42 |

|   |      | 4.3.2    | Runtime non-invasive checkpointing    | 42 |

|   |      | 4.3.3    | Background Process Image Verification | 44 |

|   |      | 4.3.4    | Program State Bookkeeping             | 44 |

|   | 4.4  | Runtin   | ne Fault Recovery                     | 46 |

|   |      | 4.4.1    | Checkpoint Process Resuming           | 47 |

|   |      | 4.4.2    | System Call Replay                    | 47 |

|   | 4.5  | Windo    | w of Vulnerability                    | 49 |

| 5 | Eval | uation 1 | Methodology                           | 51 |

|   | 5.1  | Transie  | ent Fault Model                       | 51 |

|   | 5.2  | Reliab  | ility Metrics                     | 52 |

|---|------|---------|-----------------------------------|----|

|   | 5.3  | Transi  | ent Fault Simulation              | 54 |

|   |      | 5.3.1   | Register Fault Simulation         | 54 |

|   |      | 5.3.2   | Memory Fault Simulation           | 56 |

|   | 5.4  | Experi  | ment Setup                        | 58 |

|   | 5.5  | Bench   | mark Programs                     | 58 |

|   | 5.6  | Perfor  | mance Evaluation Methods          | 60 |

|   |      | 5.6.1   | Runtime Overhead                  | 60 |

|   |      | 5.6.2   | Memory consumption                | 61 |

|   |      | 5.6.3   | Power consumption                 | 61 |

|   |      | 5.6.4   | Transient Fault Recovery          | 62 |

| 6 | Eval | luation |                                   | 63 |

|   | 6.1  | Reliab  | ility                             | 63 |

|   |      | 6.1.1   | Window of Vulnerability           | 63 |

|   |      | 6.1.2   | Mean Time to Detection            | 67 |

|   | 6.2  | Perfor  | mance                             | 68 |

|   |      | 6.2.1   | Runtime Overhead                  | 68 |

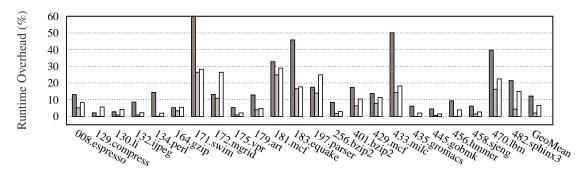

|   |      | 6.2.2   | Physical Memory Usage             | 69 |

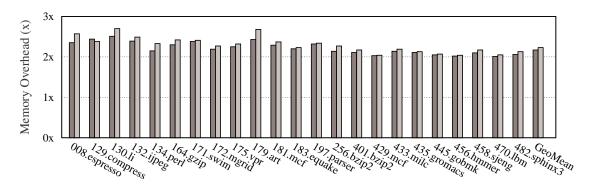

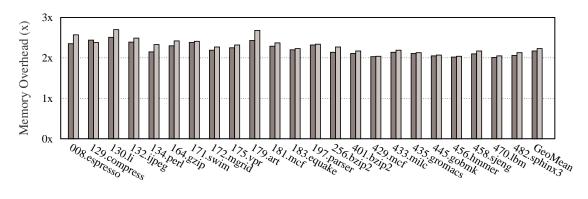

|   |      | 6.2.3   | Power Consumption                 | 71 |

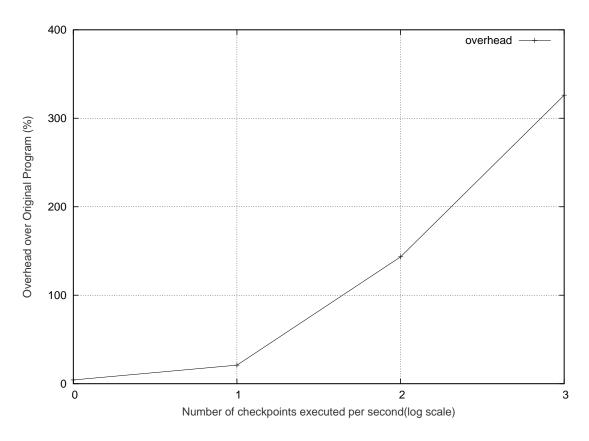

|   |      | 6.2.4   | Checkpointing Overhead            | 73 |

|   |      | 6.2.5   | Transient Fault Recovery Overhead | 73 |

| 7 | Rela | ited Wo | rk                                | 75 |

| 8 | Con  | clusion | and Future Work                   | 78 |

|   | 8 1  | Concli  | isions                            | 78 |

| 8.2 | Future Directions |   | . <b>.</b> |  |  |  |  |  |  |  |  |  |  | • |  |  |  |  |  | 7 | 19 |

|-----|-------------------|---|------------|--|--|--|--|--|--|--|--|--|--|---|--|--|--|--|--|---|----|

| 8.3 | Closing Remarks   | • |            |  |  |  |  |  |  |  |  |  |  |   |  |  |  |  |  | 8 | 31 |

## **List of Figures**

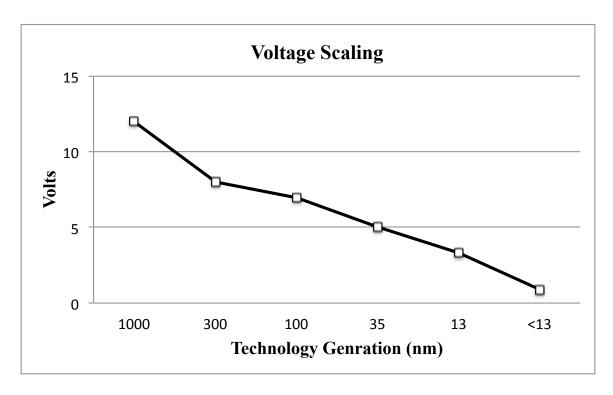

| 2.1 | Voltage scaling over generations of micro-processors. * Data source: Intel . | 11 |

|-----|------------------------------------------------------------------------------|----|

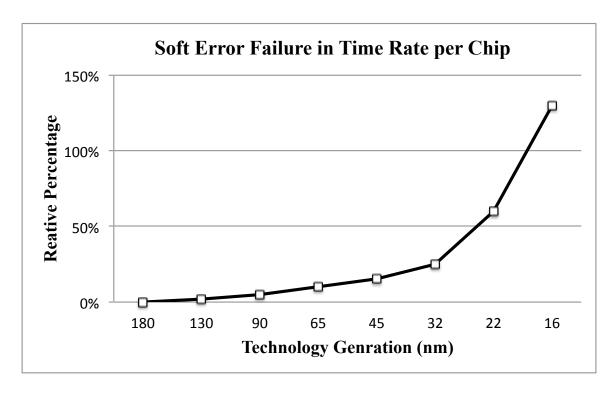

| 2.2 | Technology trend and soft error failures in time. *Data source: Intel        | 12 |

| 2.3 | Simplified Code Example from SPECINT 2000 Benchmark 183.equake               | 16 |

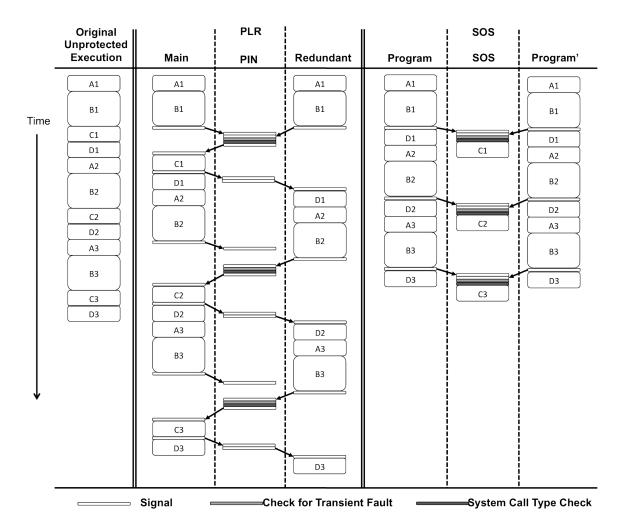

| 2.4 | Execution plan of transient fault detection without and with speculation for |    |

|     | example program in Figure 2.3 with timesteps = 3. The execution time         |    |

|     | of same instruction blocks, such as B1, B2, are slightly different across    |    |

|     | both processes because of various runtime factors such as cache behavior     |    |

|     | and process scheduling.                                                      | 17 |

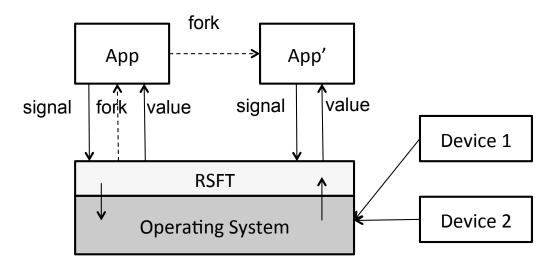

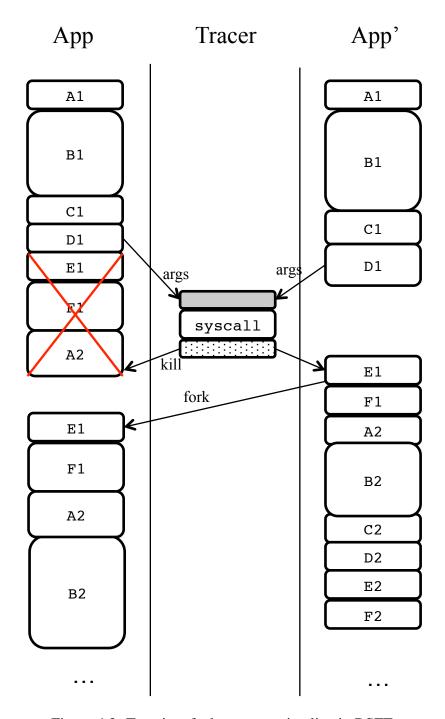

| 3.1 | RSFT-Detect Structural Overview                                              | 24 |

| 3.2 | System Call Intercepting Mechanism                                           | 25 |

| 3.3 | Misspeculation detection and recovery process in RSFT-Detect                 | 31 |

| 4.1 | RSFT-Recover Structure Overview. Dashed line indicates forking a child       |    |

|     | process then transfers tracing control to other processes                    | 43 |

| 4.2 | Transient fault recovery timeline in RSFT                                    | 48 |

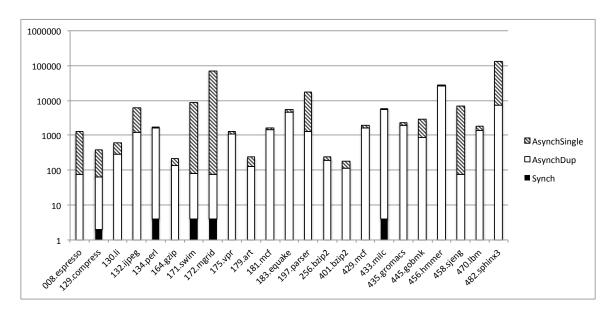

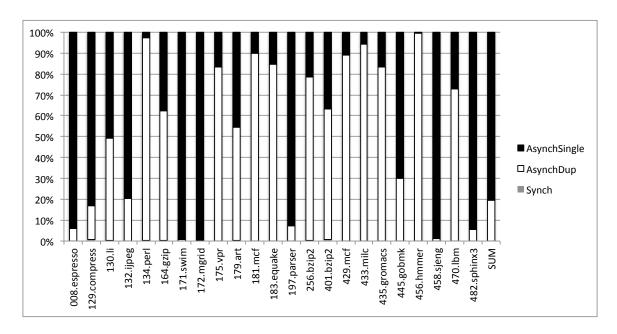

| 5.1 | Number of system calls in each benchmark (log scale)                         | 59 |

| 5.2 | Normalized System Calls Categories in each benchmark                         | 60 |

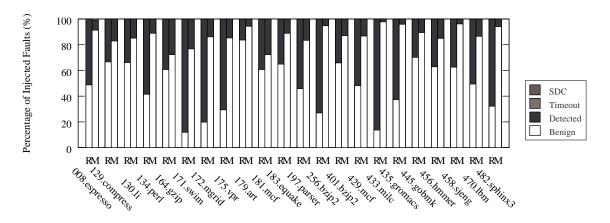

| 6.1 | Register (R) and Memory (M) Transient Fault Distribution                     | 64 |

| 6.2 | Mean time to detection for RSF1-NoSpec and RSF1with and without fault  |    |

|-----|------------------------------------------------------------------------|----|

|     | recovery                                                               | 67 |

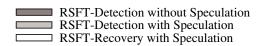

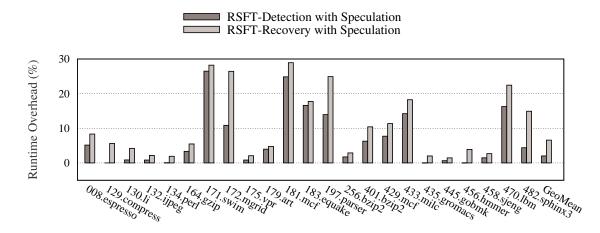

| 6.3 | Performance overhead for RSFT-Detect with and without speculation, and |    |

|     | RSFT-Recover                                                           | 69 |

| 6.4 | Physical memory overhead for RSFT with and without fault recovery      | 70 |

| 6.5 | Physical memory overhead for RSFT with and without fault recovery      | 72 |

| 6.6 | Power consumption overhead for RSFT with and without fault recovery    | 72 |

| 6.7 | Checkpointing overhead for RSFT with and without fault recovery        | 74 |

## **Chapter 1**

## Introduction

Reliability is one of the more critical concerns of a computer system. Computations on a hardware system are supposed to be calculating the correct value, as fast as possible. However, computer systems may fail due to hardware errors or transient faults. Transient faults, also known as soft errors, are caused by either environmental events, such as particle strikes, or fluctuating power supply, and are nearly impossible to reproduce. Transient faults are not necessarily attributed to design flaws and occur randomly after deployment. These faults do not cause permanent hardware damage, but may result in a complete system failure or data corruption.

In 1978, Intel Corporation first reported transient faults occurrence when its chip packaging modules were contaminated by uranium from a mine nearby. Hewlett Packard reported that the servers in Los Alamos National Laboratory were frequently crashing from transient faults resulted from cosmic ray strikes [28]. IBM S/390 [51], Boeing 777 airplanes [65], and HP's Himalaya [18] all incorporate redundant hardware for fault detection and recovery.

While transient faults are already a concern of modern computer systems, they will become a bigger problem in the future generations of architectures. As semiconductor technology continues to scale, the number of transistors on a single chip grows exponentially. As the chip area remains relatively constant, the density of transistors on a single chip is increased significantly. While the increasing number of transistors benefits processor performance, Increasing density of chips increases the chance that a particle strike affecting one transistor. Furthermore, the exponential reduction in transistor size and reduced noise margin of each transistor make them even less reliable. Moreover, extreme demands for energy efficiency drive aggressive voltage scaling, which leads to an even lower noise margin therefore less reliability. All of these technology trends make processor chips more susceptible to transient faults than ever before.

Due to the emerging requirement for reliable systems, transient fault tolerance has become one of the critical concerns in the semiconductor industry. A more recent study shows that a BlueGene/L machine with 104 nodes deployed in Lawrence Livermore National Labs experiences soft errors once every four hours [9]. For fast and reliable computation, it is critical to find efficient and low-overhead transient fault tolerance solutions for modern and future architectures.

## 1.1 Limitations of Existing Fault Tolerance Techniques

Due to the nature of transient faults, the common practice for fault tolerance is redundancy. Either the hardware module itself, or the computation on top of the hardware, is duplicated and compared against each other to verify the correctness of values. There have been two approaches, hardware and software. The hardware approach either duplicates hardware, or uses additional hardware to duplicate software execution, and the software approach duplicates program execution on the system.

Hardware solutions usually introduce extra hardware components, typically specialized for processors or storage systems. For example, caches and memory subsystems include

extra information of error-correcting codes (ECC) to allow hardware checking for transient faults and recover at runtime. These bit-level techniques typically can protect values in memory subsystems, such as caches or main memory, against transient faults. But they are prohibitively expensive to be applied to the processors, due to the nature of frequent data updating in processors. Previous work on protecting register files using ECC is extremely costly in terms of both performance [57] and power [38]. This approach cannot be applied to, for example Arithmetic Logic Unit (ALU), without paying a significant penalty in chip area, power consumption or performance.

To solve the cost problem of ECC protection for processors, semiconductor industry has introduced redundancy for processor cores or hardware contexts [15, 18, 30, 41, 46, 47, 51, 61] to provide transient fault tolerance. Compared with the ECC or parity approaches, this hardware redundancy does not have to validate data at each computation and update parity information. These techniques can validate less frequently and reduces extra hardware required for error correction. This is commonly deployed in reliability-critical systems, especially server systems, such as the Compaq NonStop Himalya, IBM S390, and Boeing 777.

However, all hardware approaches involve extra hardware components, thus adding higher cost at design and validation time. In addition, the scope and mechanism of protection are hardwired at design time under an assumed failure model (e.g. single event upset model), and working environment (e.g. reference altitude), which may be suboptimal depending on deployment environments. Some hybrid techniques combine custom hardware extension and software redundancy [41, 60] for fault detection. Because of the hardware extensions, these approaches have the same limitations as the hardware techniques.

Current architectural trends toward multicore microprocessors naturally provide additional computing resources, thus making software redundant execution more viable than ever. Existing software proposals [35, 44, 49, 60, 67] typically insert redundant code into

a program at compile time or runtime, and check for transient faults at runtime. Among these proposals, compiler-based techniques [44, 49, 60, 67, 12] are only applicable to programs whose source codes are available. Separately compiled modules, such as libraries, cannot be protected using compiler-based techniques due to the absence of source code at compile time. Additionally, these techniques are not applicable to legacy binaries, due to the absence of original source code, or compiler compatibility problems. Runtime techniques, such as [49], use dynamic instrumentation to instrument program binaries for fault detection at runtime. But this approach still has high performance overhead due to the cost of dynamic binary instrumentation, as well as frequent program synchronizations.

## 1.2 Research Objectives and Contributions

To overcome the cost, performance and applicability limitations of the previously proposed techniques, this dissertation introduces Runtime Speculative Software-only Fault Tolerance(RSFT), a comprehensive framework that efficiently protect program execution against transient faults without requiring any specialized hardware or program source code. It works on off-the-shelf hardware platforms and legacy program binaries.

This dissertation achieves its objective by taking advantage of the following insights:

- Not all values are equally important. Some register values may never affect the output of a program or change the control flow of a program. Applications' inherent fault tolerance enables RSFT to use this information to remove unnecessary value validation code to minimize the runtime validation and communication cost.

- Cross checking values produced from the program and its redundant copy creates

data dependences between these two instances, and introduces barrier synchronization. Value speculation with high confidence during program execution can effi-

ciently remove barrier synchronizations between hardware contexts, and significantly improve program performance.

With the above two observations, RSFT speculates results of predicatable system calls, so that the original program does not have to synchronize with the redundant copy(ies) to confirm the return values. This allows maximum overlapping of program execution, inter-thread/process communication, IO operations and transient fault detection.

This dissertation first presents a transient fault detection technique that provides efficient fault detection during program runtime without requiring program modification or recompilation. RSFT-Detection is a non-invasive speculative runtime system that detects transient faults. RSFT-Detection serves as a light-weight virtual layer between an application and the underlying platform. It takes a program binary as input, and automatically executes the binary redundantly using a process monitoring tool provided by the operating system to trap every system call. The arguments of the system calls invoked from both program instances are compared for correctness. A value mismatch means a transient fault has occurred and RSFT reports this to the user. Unlike some compiler-enabled techniques that must obtain knowledge of library functions for fault detection, RSFT must only understand the relatively stable and well-defined set of system calls.

To recover from faulty program execution and continue protecting execution from transient faults after recovery, this dissertation also proposes a comprehensive and efficient fault recovery scheme, named RSFT-Recovery. The original program and its redundant copy each creates a checkpoint of themselves at the beginning of the program, and keep creating checkpoints periodically during execution. The runtime light-weight checkpointing is created using system call fork's copy-on-write provided by the operating system. One checkpoint includes two newly forked processes that are stalled for future use, and their register files. Once a checkpoint is created, the two stalled processes are probed by

another background validation process. Their register files as well as memory images are compared against each other for validation. If everything is identical, this checkpoint is considered a **valid** checkpoint, otherwise it is **invalid** and is discarded. At program runtime, if a transient fault is detected, the previous valid checkpoint is used to resume correct program execution and the faulty ones are discarded. If no valid checkpoint is available, the program rolls back to the very beginning and restarts execution redundantly.

Compare with hardware or hybrid fault tolerance approaches, RSFT provides comparable performance. However, hardware solutions can provide protection for the underlying operating systems, and a wider range of hardware modules. For mission-critical systems, such as a space shuttle, the cost associated with hardware redundancy is not a major concern, but the speed of fault recovery and the fault coverage is critical. In these cases, hardware solutions suit the fault tolerance purpose better than RSFT.

RSFT provides a cheap and effective software-only method to protect applications from transient faults, with full fault coverage. However, redundant execution costs extra resources to achieve the fault tolerance. For example, RSFT consumes twice as much memory and CPU cycles as the original unprotected program. RSFT performs best when applied to applications that are computation intensive, and on multi-core or distributed architecture where extra unused CPU resource is available. Scientific computation is a good example of a typical application that RSFT works best on. For heavy IO bound applications, RSFT may add considerable runtime overhead. In addition, as RSFT does not provide protection for execution out of an application's user space, RSFT has wider window of vulnerability for those applications. These programs are better protected using hardware solutions than software ones.

One type of IO bound application is the video/audio decoding applications, such as media players. These application have high tolerance to faults naturally, and require high processing throughput. The high fault coverage of RSFT is not necessary, and RSFT's

runtime misspeculation cost is not appealing for these applications. Compared with RSFT, other software solutions, such as symptom-based techniques, will introduce lower overhead, and provide acceptable level of fault tolerance.

A prototype of RSFT is implemented and evaluated in this dissertation. To study the reliability of RSFT, a in-depth analysis on its window of vulnerability is also discussed and measured via simulated fault injection. The performance of RSFT with fault detection and recovery are separately evaluated on a commodity hardware system.

It must be noted that the implementation of RSFT in this thesis does not support multi-threaded programs. However, this implementation can be extended to support multi-threaded programs with deterministic outputs. For applications, where non-deterministic outputs are acceptable, RSFT may raise false alarms. Research on applying RSFT to these applications and redefining faulty behavior for programs with non-deterministic outputs remains a future work of this thesis.

The contributions of this thesis are:

- Design and implementation of RSFT, the fastest transient fault tolerance technique known to date. RSFT delivers full transient fault coverage with a geomean performance overhead of 6.17% for 23 SPEC CPU benchmarks using a commodity multicore system.

- A detailed evaluation of the reliability of RSFT by injecting transient faults into both register files and memory space. This work is the first to simulate and evaluate the reliability of a software transient fault tolerance technique against memory faults.

- A transient fault tolerance framework that does not require any program modification and recompilation.

## 1.3 Dissertation Organization

Chapter 2 provides background information on transient faults, the state-of-the-art transient fault tolerance techniques and their limitations. Chapter 3 and Chapter 4 propose software-only speculative transient fault detection and runtime checkpointing and recovery techniques, respectively. Their design and implementation details are described in these chapters as well. Chapter 5 introduces the methods used for evaluation in this thesis, comparing with common practice in the field and provides rationale behind these metrics. Chapter 6 summaries a broad quantitative evaluation of RSFT on a commodity multi-core system. Finally, Chapter 8 concludes this dissertation and discusses future directions of research.

## **Chapter 2**

## **Background**

Transient faults are emerging as a critical reliability concern in microprocessors. These faults are usually caused by external events such as particle strikes, or internal events, such as power fluctuation [4, 34, 43, 48]. These events can cause additional charge to be deposited and therefore alter the value of a single transistor. Transient faults do not result in permanent hardware damage, but may lead to system failures or affect program execution.

#### 2.1 Transient Faults Problem

Transient faults have already caused significant failures in deployed computer systems. Sun Microsystems, for one, acknowledges that customers such as America Online (AOL), eBay, and Los Alamos National Labs have experienced system failures due to transient faults [5]. In 2005, a 2048-CPU Hewlett Packard server system in Los Alamos National Laboratory was frequently crashing because of transient faults caused by cosmic ray strikes [28]. In addition to causing machine crashes, recent research has also shown that soft errors can lead to the derivation of secret keys in RSA public-key cryptography [3, 7] and induce security vulnerabilities [16].

Intel [54] and IBM [68] noted that radioactive materials can change the values in storage devices of processors. Manufacturing process has been taking caution to protect hardware from being exposed to radiation. While the fault rate per bit remains relatively constant over technology generations [17], exponentially growing transistor counts, combined with aggressive voltage scaling, make microprocessors more susceptible to transient faults than ever before. Additionally, cosmic radiation effects on modern microprocessors are hard to trace and evaluate because it changes with the system's deployment environment, such as altitude, geography and periodic solar phases. A majority of solar radiation is deflected from the planet surface by the Earth's magnetic field. The amount of radiation can vary significantly depending on the geographic location.

It is also difficult to measure the failure rate after deployment due to the unpredicatability of transient faults. Previous research has shown that average failure rate per bit is between 0.01 to 0.001 per 10<sup>9</sup> hours[17, 22, 32, 56]. SPARC64 was reported to have 80% of its 200,000 latches covered by some form of fault protection [2].

Future generations of processors will be even more susceptible to transient faults. Competing factors for the reliability of individual bits in a processors suggest the failure rate per bit will remain constant for the next few generations [17, 22]. The reduction in transistor size decreases the probability that cosmic radiation will strike one single transistor, but each transistor also has a reduced critical voltage (the charge necessary to change its values), increasing the likelihood that a particle strike will affect the stored state. While the failure rate per bit is staying roughly constant, the failure rate per processor is increasing proportional to the number of transistors on a chip, which increases at an exponential rate.

Voltage scaling is also one factor that may increase the fault rate per transistor in the future. Active power consumption<sup>1</sup> of a chip has quadratic relationship with the supply voltage. As a result, the tightening power consumption constraint requires the aggressive

<sup>&</sup>lt;sup>1</sup>Active power consumption is the total power consumed minus the leakage power

Figure 2.1: Voltage scaling over generations of micro-processors. \* Data source: Intel

voltage scaling. Figure 2.1 shows the voltage scaling trend over generations of micro-processors [8]. This technology trend leads to reduced noise margins, which makes transistors more vulnerable against particle strikes and power fluctuation.

The soft error rate per chip, including processor logic and on-chip memory subsystems, is increasing with the decrease of technology node. As shown in Figure 2.2, processors produced with the 32nm technology is 50% more vulnerable than the ones made with 180nm [8]. As technology leans toward smalled logic units, the soft error rate will continue to scale up. In 2004, Borkar et al. estimates about 8% reliability degradation per bit per generation of microprocessors. It is getting more and more difficult to design and produce computer systems with reliable components today, and even so in the future.

Figure 2.2: Technology trend and soft error failures in time. \*Data source: Intel

### 2.2 Existing Methods for Transient Fault Tolerance

Fault tolerance solutions have been proposed to detect transient faults during program execution via redundant computation, and recovery from the faults. The sphere of replication (SoR) [41] is used to identify the scope of fault coverage. Values that enter the SoR must be replicated for redundancy and values that exit the SoR must be checked for faults to ensure their correctness. The implication of SoR is the scope of transient fault protection. All fault tolerance techniques proposed so far depends on redundancy, either in space or time. Table 2.1 lists most recent existing representative fault detection techniques.

#### 2.2.1 Hardware Redundancy

Hardware redundancy provides transparent fault tolerance using extra specialized hardware, such as *watchdog* processor in [26]. In reality, IBM S/390 [51], Boeing 777 air-

|                 |                   | Main   | Need   | Hard      | ware     | Spher     | re of  | Repo               | rted     |  |  |

|-----------------|-------------------|--------|--------|-----------|----------|-----------|--------|--------------------|----------|--|--|

| Approach        | Technique         | Memory | Source | Con       | texts    | Replic    | ation  | Overhead           |          |  |  |

|                 |                   | Usage  | Code   | Detection | Recovery | Processor | Memory | Detection          | Recovery |  |  |

|                 | SWAT [25]         | 1×     | No     | 2         | 2        | Most      | None   | 5%                 |          |  |  |

| Specialized     | AR-SMT [46]       | 1×     | No     | 8         | -        | All       | None   | 16.7% <sup>†</sup> | -        |  |  |

| Hardware        | CRT [30]          | 1×     | No     | 2         | -        | Most      | None   | Unreported         | -        |  |  |

|                 | SRT [41]          | 1×     | No     | 2         | -        | Most      | None   | Unreported         | -        |  |  |

|                 | Hybrid-SRMT [60]  | 1×     | Yes    | 2         | -        | Most      | None   | 19%†               | -        |  |  |

| Thread-local    | EDDI [35]         | 2×     | Yes    | 1         | -        | Most      | All    | 52.2%              | -        |  |  |

| Duplication     | SWIFT [44]        | 1×     | Yes    | 1         | -        | Most      | None   | 45% <sup>†</sup>   | -        |  |  |

|                 | Shoestring [12]   | 1×     | Yes    | 1         | -        | Most      | None   | 15.8% <sup>†</sup> | -        |  |  |

| Redundant       | SRMT [60]         | 1×     | Yes    | 2         | -        | Most      | None   | 400%               | -        |  |  |

| Multi-Threading | DAFT [67]         | 1×     | Yes    | 2         | -        | Most      | None   | 38%                | -        |  |  |

| Process-based   | PLR [49]          | 2×     | No     | 2         | 3        | Most      | Some   | 16.9%              | 41%      |  |  |

| Redundancy      | RSFT[This Thesis] | 2×     | No     | 2         | 2        | Most      | All    | 3.54%              | 6.17%    |  |  |

Table 2.1: Comparison Among Transient Fault Tolerance Techniques. † indicates the results was obtained on a simulator, not commodity hardware.

planes [65], and HP's Himalaya [18] all incorporate triple-redundant hardware for fault detection and recovery on-the-fly.

However, redundant execution in custom hardware can increase the transistor count of a processor by 20-30%. This also leads to extra chip area and verification cost [2, 51]. For example, AR-SMT [46], SRT [41], and CRT [30] all use at least one or more processing unit for transient fault detection only. Additionally, the scope and mechanism of protection are hardwired at design time under an assumed failure model (e.g. single event upset model), and working environment (e.g. reference altitude), which may be suboptimal depending on deployment environments.

One hardware solution, named SWAT [25], is a symptom-based fault tolerance technique. It detects transient faults by observing the program behavior at runtime using an assumed-to-be faulty-free processor. If a program crashes, SWAT will report it and recover from a previous checkpoint, which is also assumed to remain intact after the checkpoint is made. This approach also does not handle Byzantine failures <sup>2</sup>, which is more difficult to detect than program crash.

Early multi-threaded fault detection techniques rely on specialized hardware to execute

<sup>&</sup>lt;sup>2</sup>Byzantine failures means program runs and completes even it is affected by faults. Programs with this kind of failure does not crash, but will produce erroneous, random or even malicious results.

redundant copies of the program for transient fault detection and recovery. Rotenberg's AR-SMT [46] is the first technique to use simultaneous multi-threading for transient fault detection. An active thread (A) and a redundant thread (R) execute the same program at runtime, and their computation results are compared to detect transient faults. This method uses an 8-way simultaneous multi-threading trace processor to achieve its purpose. Simultaneous Redundant Threading (SRT) [41] and Chip-level Redundant Threading (CRT) [30] exploit simultaneous multi-threaded processors and multiple cores respectively for redundant execution and value checking. These techniques use duplicate hardware modules, and check values when they escape the SoR for fault detection. Limited by its specialized hardware requirement, these approaches are also not widely adopted.

For caches and memory subsystems, extra information of error-correcting codes (ECC) is a common practice to allow hardware checking for transient faults and recover at runtime. This bit-level technique typically protects values in memory subsystems, such as caches or main memory, by encoding the bits and verifies the value against transient faults. Although this is effective to tolerant single-bit-flip transient faults, they do not work well against multiple bit flip events. Additionally, they are prohibitively expensive to be applied to the processors, or on-chip caches, due to the nature of frequent data updating in processors. Previous work on protecting register files using ECC is extremely costly in terms of both performance [57] and power consumption [38]. Similar results have been found for on-chip cache ECC protection as well. Systems with ECC protected caches suffers nearly 2% performance degradation, and 15% chip area increase. With the increase of on-chip cache size and exponentially increasing transistor count of processors, protecting processors and on-chip caches means paying a significant penalty in chip area, power consumption, performance, or all of the above.

#### 2.2.2 Software Redundancy

Compared with hardware redundancy approaches, software-only solutions are more appealing for its cost-efficiency and flexibility [15, 30, 44, 60, 35]. Although software solutions also use some extra resources for redundancy, they usually do not require specialized hardware modules. Instead, these techniques exploit redundancy using existing underemployed processors, register files or cores to achieve redundancy. Software transient fault detection techniques typically fall into three categories: thread-local duplication, redundant multi-threading and process-based redundancy, as shown in Table 2.1. Thread-local duplication techniques such as EDDI [35] and SWIFT [44] redundantly execute instructions within a single thread, exploiting instruction-level parallelism to improve performance. Shoestring [12] combines symptom-based fault detection with selective instruction duplication to achieve lower overhead than both EDDI and SWIFT, but with lower fault coverage. Redundant multi-threading techniques (e.g. SRMT [60] and DAFT [67]) use multiple threads to execute program codes redundantly. Process-based redundant techniques (e.g. PLR [49]) use multiple processes instead of threads, at the cost of maintaining multiple memory states.

All these techniques are typically implemented using either compiler transformations or runtime systems. Compiler-based approaches toward transient fault detection, such as EDDI [35], SWIFT [44], SRMT [60], DAFT [67], and Shoestring [12], all require program source code for recompilation, and cannot detect any transient fault occurring in separately-compiled modules.

EDDI [35] provides fault tolerance for programs via instruction duplication within the same thread. Each memory location has a corresponding shadow location in memory for duplicated instruction, which increases memory pressure. SWIFT [44] also exploits unused computing power of multiple-issue processors by duplicating program execution within

Figure 2.3: Simplified Code Example from SPECINT 2000 Benchmark 183.equake

the same thread. Achieving low runtime overhead for fault detection, SWIFT-transformed codes require twice as many registers, potentially causing register spills. In SWIFT, memory operations can only be performed once due to potential side effects. Transient fault checking instructions must be inserted before every memory operation. Unlike SWIFT, RSFT exploits multiple cores for redundant execution to minimize runtime overhead, and utilizes separate memory spaces provided by multiple processes to eliminate per-memory operation fault checking.

Software-based Redundant Multi-threading (SRMT) is a software solution that achieves redundancy with multiple threads. The SRMT techniques uses compiler transformation to automatically generate redundant code for runtime fault detection. However, due to the single memory state maintained during execution, redundancy is lost at memory operations. These techniques cannot issue redundant store instructions because only one shared memory state is maintained. Before a memory operation is executed, its operands are communicated between threads and checked for consistency. Consequently, frequent barrier synchronization is required and adds significant performance cost. When a real transient fault triggers an exception, SRMT invokes the program's exception handler to catch the fault, registering a false positive and possibly changing the program's behavior.

Compared with compiler-based techniques, runtime techniques do not require any program source code to be recompiled and can detect transient faults for separately compiled modules as well. One such implementation called PLR [49], a dynamic instrumentation technique, provides transient fault detection with the minimum runtime overhead (16.9%)

Figure 2.4: Execution plan of transient fault detection without and with speculation for example program in Figure 2.3 with timesteps = 3. The execution time of same instruction blocks, such as B1, B2, are slightly different across both processes because of various runtime factors such as cache behavior and process scheduling.

among all software solutions with full coverage. This technique duplicates the original program into several instances at runtime, maintaining one private memory space for each instance. Only externally visible values need to be verified before they escape user space.

PLR duplicates the execution of the application and its libraries, protecting program execution on both processors and memory, but not in the operating system. As a result, the arguments of a system call escape the SoR and must be checked before the system call is executed in kernel mode. Similarly, the return value of the system call is an input to the SoR, and needs to be replicated in both program instances. Therefore, PLR synchronizes the main and the redundant processes at every system call for transient fault detection and returns replicated value. The main process executes the system call. The redundant process only resumes execution after the system call is completed. This barrier synchronization puts inter-core communication on the critical path of program execution, leading to slower performance.

Other techniques, such as the pi bit [64] proposed by Weaver et al. and dependence-based checking [58] by Vijaykumar et al. detect faults that affect program behavior. This is done by following the propagation of faults through the entire program. For optimal performance, these techniques have to use herotic alias analysis to find the minimum set of dependences that fault tolerance code must track at runtime. RSFT achieves the same goal by only detecting non-benign faults only when they are about to affect program output. No program source code or alias analysis is needed to analyze the fault propagation ahead of time.

## 2.3 Limitations of Existing Techniques

Hardware redundant computing requires extra chip area, extra logic units, and additional hardware verification. The scope of protection and fault detection scheme are usually hard-

wired at design time, which limits the system's flexibility. On the other hand, software redundancy is more flexible and much cheaper in terms of physical resources. Software approach avoids expensive hardware and chip development costs. The ongoing multicore design provides increasing parallel resources in hardware, making software redundancy solutions more viable than ever.

Although software approach is more appealing, the significant runtime overhead of existing software techniques prohibits the previously proposed schemes from being deployed on commodity multi-core systems. For example, SRMT [60], a compiler-assisted redundant multi-threading implementation, adds 19% performance overhead, even with specialized hardware communication queue. PLR [49], as an example of runtime technique using process level redundant execution, adds 16.9% average runtime overhead for un-optimized programs, and much more overhead on IO intensive applications.

This dissertation proposes RSFT, the first speculative transient fault tolerance framework that provides the fastest transient fault detection and recovery. RSFT automatically duplicates program execution in a non-invasive way. As a result, RSFT maintains replicated memory states and has the SoR that covers both the processor cores and the memory subsystems. It eliminates frequent barrier synchronization via speculation, and provides efficient recovery mechanisms after a transient fault is detected. Compared with previous work, RSFT yields the lowest performance overhead for transient fault detection without compromising fault coverage.

To illustrate the advantage of RSFT, Figure 2.3 shows a simplified code example from 183.equake, a SPECFP 2000 benchmark program. Figure 2.4 compares non-speculative execution plan versus speculative execution plan in RSFT. These execution plans demonstrate that barrier synchronizations add considerable runtime overhead to the program. Although both process instances are executing the same program binary, the cycles spent on executing each piece of code, such as B1, B2, ..., are not the same because of various

runtime factors such as cache behavior and process scheduling. Forcing barrier synchronization at every system call accumulates such timing difference, consequently slows down the whole program execution. In contrast, RSFT allows one process to speculate the return values of sys\_write system call without actually executing it, therefore does not require waiting till the other process to invoke the same system call and the barrier synchronization between several program instances. If a misspeculation occurs, an efficient misspeculation recovery scheme is employed to continue execution from a previous verified program state. Combining all the features above, RSFT achieves very low runtime overhead with full fault coverage.

To understand and compare the performance of PLR, the best performing software transient fault tolerance technique, this thesis also implemented an approximation of PLR called RSFT-NoSpec. The implementation of RSFT-NoSpec faithful replicates the original paper, but using the light-weight processing monitoring tool utilized in RSFT, instead of PIN, the dynamic binary instrumentation employed in the original paper. As shown in Figure 2.1, RSFT-NoSpecis a lower-bound approximation of PLR with regard to the performance overhead.

## **Chapter 3**

## **Runtime Speculative Transient Fault**

## **Detection**

This chapter introduces the transient fault detection mechanism in RSFT, called RSFT-Detect [66]. Compared with previously proposed fault detection work, this technique does not require program source code, runtime instrumentation or program recompilation. RSFT-Detect is a fast and effective transient fault detection system that exploits the efficiency and functionality of an OS-level process monitoring tool ptrace. The ptrace utility is a POSIX standard that is provided by Linux/Unix, Mac OS, and Solaris systems to provide process monitoring and debugging capabilities. This kind of monitoring utility is exploited in RSFT-Detect as a method of trapping system calls and comparing the values of their arguments to detect transient faults. This approach ensures that RSFT-Detect can transparently detect transient faults occurring in a non-invasive way.

This chapter first discusses the existing research on transient fault detection, and compares RSFT-Detect with other alternative techniques. Section 3.2 describes the overall structure of RSFT-Detect. The following sections details the technique and its implementation. Section 3.11 discusses the window of vulnerability of RSFT-Detect, and compares

#### 3.1 Related Work

Software-only transient fault detection techniques are advantageous compared with hardware approaches because of their flexibility and no extra hardware design cost. They are typically cheaper and easier to deploy on a commodity systems.

Among existing software transient fault detection techniques, many proposals use the compiler to recompile application code and insert proper instructions for transient fault detection. While these techniques can obtain a global view of the program code and instruction dependences to further optimize code for performance, they are limited by the need for the program source code. Separately compiled modules, such as existing libraries, often do not have source code available for recompilation. Thus, these separately compiled modules are a part of the window of vulnerability of these techniques. Previous compiler-based fault tolerance techniques do not evaluate their fault coverage when processors are running library code.

Another approach, being aware of such limitations, proposes to instrument program binary code at runtime for transient fault tolerance [49]. Although this approach protects program and its dynamically linked binaries, it suffers from high overhead incurred by the dynamic instrumentation. For example, Pin instrumentation framework, which was used in PLR [49], is reported to add 20-30% runtime overhead on average, just through executing a program binary within the framework. The evaluation in this dissertation runs all SPEC benchmark programs within the PIN dynamic instrumentation framework, and proves the estimates. The average performance overhead of PIN is 44.54% across all benchmark programs. The barrier synchronization in PLR further adds 17.27% more overhead on top of that.

#### 3.2 Overview

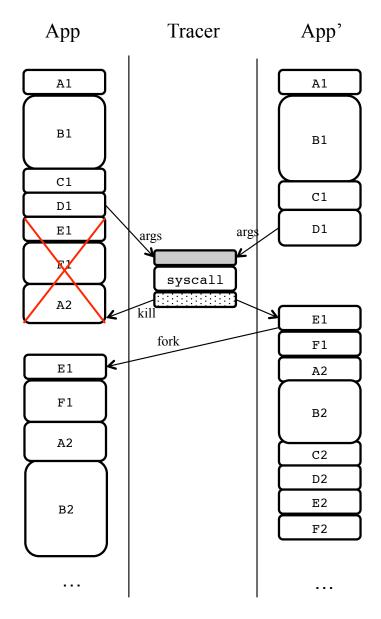

Unlike all previous proposals, RSFT-Detect utilizes a process monitoring utility (ptrace) to intercept system calls invoked by a program. As a light-weight interface between the operating system and user applications, ptrace adds very little runtime overhead. Figure 3.1 demonstrates the overall structure of RSFT-Detect and the interaction between several components of the system. RSFT-Detect first takes the program binary and its input, then spawns one process that execute the binary redundantly. Upon process creation, RSFT-Detect immediately pauses that process, and inject a fork system call into the just-created child process App. The child process App spawns another process App' from itself, inheriting all its virtual address table and signal handling table. This is critical to eliminate potential false-positives, especially on systems with address space randomization enabled. From then on, App gives up its parent-ship of App' to the tracer process. Both App and App' becomes processes that are traced only by the tracer process RSFT-Detect.

During the execution, RSFT-Detect serves as a virtual layer between the application and the underlying OS services and devices. It traps every system call invoked by either program instance. After a system call is trapped, the process's register file is examined to find out the type of the system call. RSFT-Detect then compares the system call's arguments against those in the other program instance to check for transient faults, if available, according to its specific calling context. If the system call reads a process' memory space through pointer arguments, the memory content is also checked. If no transient fault is detected, RSFT-Detect executes the system call and lets the program instance continue execution. This runtime system predicts the results of system calls when possible, which allows speculative execution of the program. When misspeculation is detected after a system call is completed, misspeculation recovery schemes are employed to ensure continuous correct execution of both program instances.

Figure 3.1: RSFT-Detect Structural Overview

# 3.3 Automatic Process Duplication

As shown in Figure 3.1, RSFT-Detect first fork a new process from itself, and starts executing the binary with its arguments in the newly create process. Algorithm 1 describes the detailed steps of how to force a child process W1 to create a copy of itself and gives up its parent-ship to RSFT-Detect.

#### **Algorithm 1** Non-invasive Process Duplication

- 1: W1.pid = fork()

- 2: copy original register file of W1

- 3:  $W1.Regs.rax = SYS_fork$

- 4: // the instruction SYSCALL is OF 05, which takes 2 bytes

- 5: W1.Regs.rip = W1.Regs.rip-2

- 6: continue executing the system call

- 7: // program will re-enter interrupt and execute system call fork

- 8: wait for kernel finishes executing *SYS\_fork*

- 9: W2.pid = W1.Regs.rax

- 10: copy back original register file of W2

- 11: continue executing W1 and W2

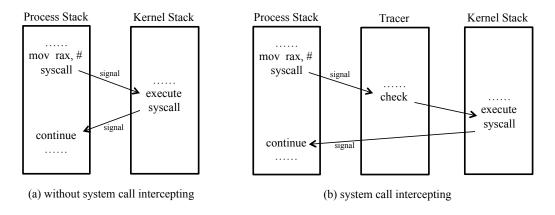

Figure 3.2: System Call Intercepting Mechanism

# 3.4 System Call Trapping

RSFT-Detect detects transient faults at system call interface level. The idea is to intercept all system calls initialized from two identical program instances. There is a fixed set of well-defined system calls provided by the operating system to applications. For modern Linux operating system, a total of 298 system calls are defined. It is reasonable to specify customized system call arguments verification for each system call.

RSFT-Detect serves as a thin layer between programs and the underlying system and hardware devices. Figure 3.2 illustrates the process of system call intercepting and argument verification process. Depending on the type of the arguments, different checking methods are used, including value comparison and memory content comparison. As the interface of system calls are very well defined, all system call arguments must be a register value. If an argument is a pointer, the size of the pointed to content must be specified in the system call arguments as well. Operating system itself also leverages this knowledge to handle the user space memory content. As a result, it is possible to manually inspect all system calls, and write speculation code for each system call by hand.

Despite the redundant execution of program binaries, side-effecting work should only happen once. Since system calls have well defined interfaces and calling contexts, it is

|        | Duplicate | Speculation | Example                                 | Distribution in SPEC |

|--------|-----------|-------------|-----------------------------------------|----------------------|

| Sync   | No        | No          | sys_read(0), sys_readv(0), sys_lseek(0) | 0.01%                |

| Asynch | Yes       | No          | sys_mmap, sys_mremap, sys_brk           | 19.33%               |

|        | No        | Yes         | sys_write, sys_writev, sys_setitimer    | 80.66%               |

Table 3.1: Categorized System Calls

possible to manually examine all system calls and select out the side-effecting ones. For example, a fprintf (which transitively calls a write system call) can not be redundantly executed. Based on whether the results of the system call can be speculated and whether the system call needs to be executed in both copies of the program instances, all system calls are categorized into four categories. Table 3.1 gives the classification and some examples from existing system calls. The last column gives the distribution of system calls among these four categories, sampled from SPEC benchmark programs. RSFT-Detect handles system calls differently depending on which category they belong to.

- Synchronize: This category includes system calls that have no predictable program state after system call execution. These system calls cannot be executed redundantly (e.g. sys\_read that writes data to memory). Some read operations, such as destructive read from standard input or other devices, can only be executed once. After the read, the content will be destroyed and not be available for a redundant read. RSFT-Detect can tell this kind of read from the file descriptor argument of sys\_read call. RSFT-Detect must conduct sys\_read system call only once, and copy the data to both program instances' private memory space to ensure identical program state in the subsequent execution. sys\_lseek has the same semantics that need to be respected.

- Asynchronize duplicate: Some system calls, such as sys\_brk, have no predictable return values, but its execution and return values must be duplicated in both program instances to ensure correct program execution. These system calls need to have

identical return values in both program instances, but barrier synchronization is not necessary. RSFT-Detect handles this kind of system calls by allowing the first instance that invokes the call to execute the call and keeps a record of its return values. When the other instance invokes the same call, RSFT-Detect compares their arguments for faults detection, then enforces the call to do the same work in the second instance. In the example of sys\_times, the recorded return value is returned to the second instance.

• Asynchronize single: This category includes system calls with return values that can be speculated with high confidence, but cannot be executed redundantly, such as sys\_write. Among all system calls invoked dynamically on SPEC benchmark program, 72.59% calls belong to this category. RSFT-Detect does not require barrier synchronization for these system calls. If one copy of the process invokes sys\_write ahead of the other process, it can continue executing the rest of the code without waiting for the system call to complete. When the other process reaches the point of issuing sys\_write, it will compare the arguments of this system call and the memory content it is going to write for fault detection. If any fault occurs, RSFT-Detect is still able to report the fault to users.

# 3.5 Speculation

Previous work on transient fault detection, such as PLR proposed by Shye et al. [49], also explored the method of monitoring program execution at system call level to find mismatched arguments. However, these approaches conservatively require both processes (the original and the redundant) to synchronize at each system call. Some system calls can be executed redundantly, while some cannot. Both processes are allowed to continue execu-

tion only after non-redundant system call returns from the kernel, when its return value is duplicated and sent to both processes for further computation. This kind of barrier synchronization adds considerable overhead to program execution time. Evaluation in Chapter 6 discusses the performance in details.

RSFT-Detect, on the other hand, does not require barrier synchronization between processes when the results of the system call can be speculated. For example, in line C in Figure 2.3, printf invokes system call sys\_write, which returns the number of bytes transmitted if it succeeds. RSFT-Detect always speculates the return value to be the number of bytes supposed to be transmitted according to the input parameter. The first program instance that invokes this sys\_write call is allowed to continue execution without waiting for this system call to complete, as shown in Figure 2.4. This system call is only executed by the kernel when the other program instance also invokes the same call. This high-confidence value speculation allows one process to proceed without waiting for the other process or the system call to complete in kernel mode. A large set of the existing POSIX system calls such as sys\_write, sys\_munmap can be speculated in this way.

# 3.6 Misspeculation Detection and Recovery

Misspeculation occurs when the results of a system call differs from what RSFT-Detect predicts. This means the speculatively executing program instance must be discarded due to a wrong prediction made earlier. RSFT-Detect features a fast misspeculation detection and recovery scheme to restart program execution from the point of misspeculation.

In order to efficiently record program state, RSFT-Detect exploits system call forks copy-on-write semantics. If the tracing process detects misspeculation, it kills the speculative process and duplicate the non-speculative process for later computation. Copy-on-write semantics have previously been used to implement speculative systems [40]. Com-

pared with transactional memory, this approach has less speculative overhead.

To inject a fork system call into the no-speculative process, without rewriting program's binary, RSFT-Detect follows the algorithm described in Algorithm 2. In the following algorithm, W1 refers to the first invocation of the program binary, W2 refers to its replicate, and W refers to either one of the worker processes (W1 or W2).

#### Algorithm 2 Misspeculation Detection and Recovery

```

1: repeat

2:

intercepts system call sys from a traced process W(either W1 or W2)

// Code for fault detection

3:

if sys's return value was speculated in W2 then

4:

5:

// symmetric if W1 is the speculative process

if W1.Regs.rax != W2.specvalue[sys] then

6:

kill(W1.pid, SIGKILL)

7:

// duplicate the non-speculative process W2

8:

9:

make a copy of the register file of W2

W2.Regs.rax = SYS_fork

10:

// the instruction SYSCALL is OF 05, which takes 2 bytes

11:

W2.Regs.rip = W2.Regs.rip-2

12:

continue executing the system call

13:

// program will re-enter interrupt and execute system call fork

14:

wait for kernel finishes executing SYS_fork

15:

W1.pid = \text{return value}

16:

copy back original register file of W2

17:

18:

continue executing the program

end if

19:

end if

20:

21: until W1 and W2 both exit

```

For the code example in Figure 2.3, RSFT-Detect speculates the number of bytes being transmitted by system call <code>sys\_write</code> and allows the process arriving first to proceed without waiting for the other process. When the other process calls <code>sys\_write</code>, RSFT-Detect executes <code>sys\_write</code> and then compares the return value with the speculated value. If the two values are the same, both processes proceed normally. Otherwise, misspeculation happens. The recovery process is demonstrated in Figure 3.3. When misspeculation is

detected upon the return of the real system call (as shown in Figure 3.3), RSFT-Detect sends a signal to kill the misspeculated process. Another signal is sent to the program instance with correct values to force a fork system call. A new process is then spawned from Program, and continues the rest of program execution redundantly with the correct program state.

# 3.7 Virtual Memory Space Synchronization

To compare execution of two processes, the original one and its redundant copy, the fault detection may have to compare some virtual memory addresses at some system call. This is crucial to ensure identical memory layout of all processes to eliminate false-positives. As a result, some system calls, such as sys\_mmap, must be executed in all copies of processes for a program to continue. Additionally, these two processes must have identical virtual address table to start with. In systems with address space randomization (ASR), independence processes have randomized virtual address mapping even for executing the same program binary.

One solution to this problem is to disable address space randomization entirely by configuring the operating system. However, this also disables the ability of other applications, for example security sensitive applications, from benefiting from ASR.

RSFT-Detect solves this problem by allowing the first process that reaches sys\_mmap to execute first. Upon returning from the system call, RSFT-Detect keeps a record of the virtual memory address that this call allocates in this process. When the other the process invokes sys\_mmap, RSFT-Detect first compares their arguments for transient fault detection, then forces this call to map to the same virtual address as the first process, by setting the MAP\_FORCED flag. Because both processes maintain the same memory layout, both processes should be in the same program state before and after the system call.

Figure 3.3: Misspeculation detection and recovery process in RSFT-Detect

There are also cases when sys\_mmap intends to map files to a process' virtual memory space and performs read and write operations. By intercepting mmap system call and checking its arguments, RSFT-Detect can identify such requests and map that file in RSFT-Detect's own memory space. RSFT-Detect then returns a protected page address to the two program instances. When these programs intend to access the protected page, a signal is sent to and trapped in RSFT-Detect. At that point, RSFT-Detect checks for transient faults, then performs the actual read and write access only once on the memory mapped file.

# 3.8 Signal Handling

In RSFT-Detect, signals sent to the program and signals raised from one copy of the program must be handled in a way that is transparent to the user. Failing to handle these signals will result in either false alarms, or incorrect program behavior. All existing software-only transient fault tolerance techniques either ignore these signals or report them as transient faults despite of what they really are. This section discusses two different types of signals and the methods RSFT-Detect take to handle them.

Internal Signal: Signals can be raised from program itself, in the absence of transient faults, either as a program bug or designed the program behavior. However, some transient faults can cause a program to raise an unexpected internal signal. For example, a particle strike may flip a bit in a register that holds a memory address the program loads from. Note that the two identical program instances do not share memory space and have different set of register files. Consequently, a transient fault may cause a segmentation fault raised by one of the processes, but not both of them. Similarly, other exceptions, such as divide-by-zero, may also occur as a result of a transient fault. To distinguish a transient fault from a normal internal signal raised by the program, such as signals caused by program bugs, RSFT-Detect traps all signals raised by both processes. If the two processes both raise

the same internal signal, it is an expected signal and must be handles in the default way.

Otherwise, RSFT-Detect alerts the users the existence of a transient fault.

External Signal: As a transparent transient fault detection technique, RSFT-Detect maintains the original deterministic behavior of the original program. External signals may cause non-determinism among the two copies of programs. For example, the user may press ctrl-c from command line, which sends a SIGINT signal to the program. RSFT-Detect should make sure the two program copies behave as if only one program is running and abort the program.

To achieve this, RSFT-Detect registers special signal handlers for all external signals. Specialized signal handlers are registered at the beginning of the program. When an external signal is received, the corresponding signal handler is called and proper actions are taken. For example, in the case of a SIGINT sending to the program from command line, RSFT-Detect communicates SIGINT to both processes, terminates their execution and kills itself as well.

There are cases where one fault process may bypass the signal raising code. RSFT features a timeout watchdog process, which will raise timeout signal if the program has not made progress after a pre-defined threshold. RSFT will handle this case as a transient fault. This threshold is typically application specific. In the evalution of this dissertation, the threshold was set to ten times of a typical run's execution time.

# 3.9 Optional Memory Page Walking

To protect program execution from transient faults in memory sub-systems, RSFT-Detect adopted process-level duplication and use redundant memory space. However, two processes, one forked from another, share the same physical memory page, if no value is written to that page. As a result, memory faults occurring in pages that are shared by the

two processes can be read by both program copies hence introducing faulty values. This means the two copies will produce the same faulty results, which may cause the system to fail severely.

RSFT-Detect solves this problem, by optionally turning on a knob to perform automatic memory page walking. The idea is to check the two processes' physical page table periodically. If any of the pages that are physically in memory has the same physical page address for both processes, RSFT-Detect automatically loads a word from the page, and immediately writes the same value back, utilizing the copy-on-write feature of forked processes. The operating system will automatically create another physical page as a tainted copy.

There is a trade-off between memory consumption and memory fault coverage. By enabling memory page walking, there is a better chance for RSFT-Detect to detect memory transient faults, at the cost of using more physical memory during redundant execution. Disabling this memory page walking will reduce the size of active physical memory usage, but results in larger window of vulnerability in practice.

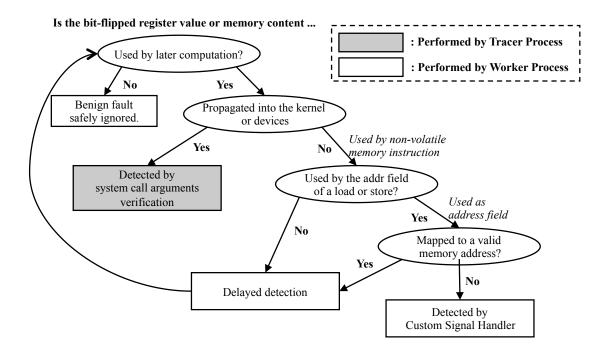

### 3.10 Transient Fault Detection

A combination of the above techniques gives RSFT-Detect the ability to detect a wide range of transient faults in both processor and memory subsystems. Figure 3.10 lists several results of transient faults, and how RSFT-Detect handles each of them.

• Register Value. A transient fault may alter a register value that never flows into the following computation of the program. These faults can be safely ignorely. If the altered register value directly changes the values that escapes the SoR, these faults can be detected via value comparion in RSFT fault detection. If a fault changes an address of a memory access operation, the program may trigger a segmentation fault. If a segamentation fault is found in only one of the work processes, this asymmetric

behavior is identified as a transient fault. Otherwise, transient fault detection will not catch this fault when it occurs. Instead, this fault will be caught in later fault detection via value comparison.

• Memory address. If a memory content is modified by a transient fault, this value can be either instruction or data. In case the value is an instruction, and will be executed, the two worker processes have high probability of executing different binary and end up sending different values out of SoR. This kind of faults is captured by RSFT. Otherwise, this altered instruction can be safely ignored. If the memory content holds a value to be loaded to the program, RSFT detects such fault like register values discussed above. Otherwise, this fault will not change the program behavior, hence not the target of transient fault detection.

## 3.11 Window of Vulnerability

A fault occurring in RSFT-Detect itself may cause an unrecoverable error or erroneous results or undefined program behavior. Additionally, RSFT-Detect does not protect the operating system and its services executed in kernel. Transient faults occurring in the kernel code may still cause program failure.

Although RSFT-Detect itself represents a single point of failure, it only occupies the CPU for a very short duration and only consumes a few clock cycles. Typically the RSFT-Detect process only takes less than 0.01% CPU time throughout program execution. The probability of transient faults occurring registers while RSFT-Detect code is running is extremely low.

The memory consumption of RSFT-Detect is 9.5MB peak. If a transient fault hits the main memory that holds data used in the tracing process, it may lead to program crash or wrong output. However, such faults may still be benign faults or be detected via transient fault detection. For example, if the fault flips a bit of a word in memory, which is overwritten before the value is loaded, the fault is a benign fault. If a memory fault changes the value of a word in memory which results in a value mismatch in fault detection code, it can also be detected.

Chapter 6 evaluates RSFT-Detect's window of vulnerability by simulating transient faults in both register files and main memory.

# Chapter 4

# **RSFT Transient Fault Recovery**

The previous chapters presented transient faults detection at program runtime using program instance duplication and runtime checking. However, detecting a transient fault is only the first step of fault tolerance. Detecting a fault only prevents program from corrupting outside visible program state and enforces data integrity. Detection alone does not guarantee un-interrupted correct program execution in the presence of transient faults. In an environment where transient faults occur frequently, users may never have a single run without transient faults corrupting critical values. A system must be able to recovery from a fault to be truly fault resilient.

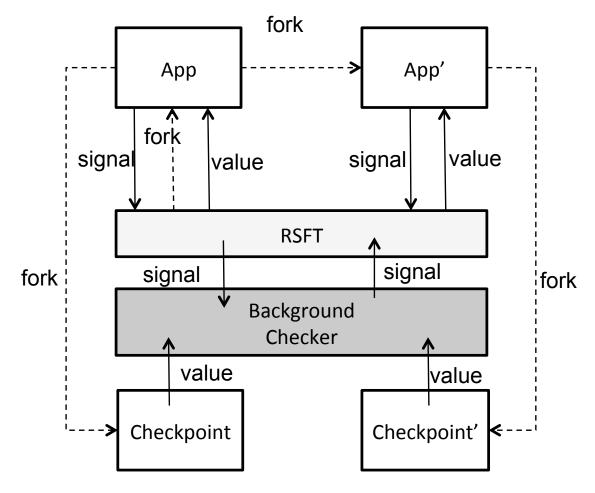

This chapter describes the transient fault recovery system of RSFT, called RSFT-Recover . RSFT-Recover is a novel program execution checkpointing and recovery system that performs cheap and fast program checkpointing, program state verification and fast program state recovery.

This chapter first introduces the background of transient fault recovery. Section 4.2 discusses several common fault recovery mechanisms proposed previously and their limitations to motivate the RSFT-Recover. Section 4.3 illustrates the overall design of RSFT-Recover. The following sections introduces the implementation details of RSFT-Recover.

Section 4.5 discusses RSFT-Recover's window of vulnerability and compare it with existing fault recovery proposals.

## 4.1 Transient Fault Recovery

After a transient fault is detected, the program may behave differently depending on the result of the transient faults.

- Benign Faults. These transient faults alter values held in registers or memory, but

does not propagate to the output or devices. The program can continue executing

and produce correct output after a fault has occurred.

- Non-benign faults. Program execution hit by a transient fault may produce erroneous